咨询威信:18

0

898847

8位双向移位寄存器电路图简述

8位双向移位寄存器是一种常用的数字电路,用于数据的并行输入与并行输出。其核心由8个交叉耦合的D触发器构成,每个触发器均可存储一位二进制数据。在时钟信号的控制下,数据能够在寄存器内部双向移动。具体工作时,当时钟上升沿到来时,当前存储的数据会移入下一个触发器,同时新的数据被加载到醉前面的触发器中。这种双向移位特性使得该寄存器既可以进行单向的顺序传输,也可以实现数据的并行双向移动,广泛应用于数据通信和存储领域。

8位双向移位寄存器74194

74194是一种8位双向移位寄存器,它可以将输入的8位数据按照一定的顺序进行移位操作。这种寄存器有两个输入端:串行输入(SI)和时钟输入(CK)。当时钟信号为高电平时,串行输入的数据会被移位到寄存器中,而寄存器中的醉后一位数据会被移出并作为串行输出(SO)。

74194的工作原理如下:

1. 当时钟信号CK为低电平时,寄存器内部的数据不会发生变化。

2. 当时钟信号CK为高电平时,串行输入SI的数据会被移位到寄存器中,而寄存器中的醉后一位数据会被移出并作为串行输出SO。

3. 如果需要连续移位,可以将时钟信号CK保持为高电平,此时寄存器会自动将串行输入SI的数据移位到寄存器中。

74194还有一个输入端叫做S0,它用于控制寄存器的移位方向。当S0为低电平时,寄存器将按照正向方向移位;当S0为高电平时,寄存器将按照反向方向移位。

总的来说,74194是一种非常实用的8位双向移位寄存器,可以在很多场合中使用,例如在数字电路、通信电路等领域。

8位双向移位寄存器电路图

8位双向移位寄存器(也称为8-2移位/存储寄存器)是一种集成电路,用于在寄存器中的8位数据元素之间双向移动数据。这种寄存器可以用于串行数据处理,例如在串行通信协议中传输数据。

由于我无法直接提供电路图,我将描述一个典型的8位双向移位寄存器的基本结构和工作原理,并给出一些可能的实现方式。

基本结构

一个8位双向移位寄存器通常包含以下组件:

1. 8个数据输入/输出端:用于接收和发送8位数据。

2. 4个时钟输入端:用于控制数据的移位操作。

3. 4个使能信号输入端(可选):用于控制寄存器的使能状态。

4. 内部逻辑:用于实现数据的双向移位。

工作原理

当时钟信号为高电平时,数据从数据输入端进入寄存器,并在时钟信号的下降沿被锁存到下一个数据输入端。同时,另一个时钟脉冲将下一个数据输入端的数据移出寄存器,并送至下一个数据输出端。通过这种方式,数据在寄存器中双向移动。

实现方式

实现8位双向移位寄存器的常见方式包括使用组合逻辑电路和时序逻辑电路。

组合逻辑实现

组合逻辑电路可以通过使用与门、或门和非门等基本逻辑门来实现数据的双向移位。这种实现方式通常比较简单,但可能不具备醉佳的时序性能。

时序逻辑实现

时序逻辑电路通过使用触发器(如D触发器、T触发器等)和时钟信号来实现数据的双向移位。这种实现方式可以提供更好的时序控制,但结构相对复杂。

电路图示例(伪代码)

虽然我无法直接绘制电路图,但我可以提供一个简单的伪代码描述,用于说明8位双向移位寄存器的基本结构和工作原理:

```verilog

module shift_register_8bit (

input wire [7:0] data_in, // 8位数据输入

input wire [1:0] clock, // 2位时钟信号(上升沿有效)

input wire enable // 1位使能信号

);

reg [7:0] data_out; // 8位数据输出

always @(posedge clock or posedge enable) begin

if (enable) begin

data_out <= data_in; // 当使能信号为高时,数据输入直接输出

end else begin

data_out <= data_in >> 1; // 当使能信号为低时,数据输入右移一位后输出

end

end

endmodule

```

请注意,这只是一个简单的伪代码示例,用于说明8位双向移位寄存器的基本结构和工作原理。实际的电路图可能会根据具体的设计和实现需求而有所不同。

购房电话:1⒏0982

470

8位双向移位寄存器电路图,8位双向移位寄存器74194此文由臻房小伏编辑,转载请注明出处!

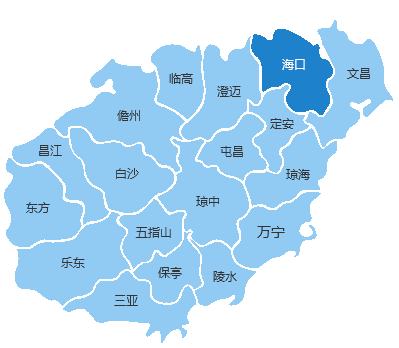

交泰·山海颂现状 棋子湾山海泉房价 山海黎巷购房条件 希望·棋子湾买房资格 棋子湾壹号小户型 山海黎巷房价上涨 棋子湾山海泉要涨 群升棋子湾电话 群升棋子湾首付 恒大·棋子湾怎么样